manudrz a écrit:Moi j'attends la partie clock, ça m'intrigue cette affaire

Tu penses mettre quoi, de l'OCXO ?

j'ai plusieurs idées en tête.

soit un Crystek à 30 balles avec son 3042 survit d'un cap multiplier.

soit une soluce hard, sur la base de l'expérience de la rutgers clock

https://www.by-rutgers.nl/rutgerS-Clock.html

ou de celle ci en mode differentiel (j'adore)

http://www.diyaudio.com/forums/group-bu ... ck-gb.html

manudrz a écrit:http://www.conwin.com/pdfs/AN2093.pdf

J'avais un doute sur son régulateur, mais oui certains collent bien 2200µF derrière un LT3042, du coup autant mettre un autre reg moins hype...A minimum 4.7µF output capacitor

with an ESR below 50mΩ and an ESL below 2nH is

required for stability.

Par contre j'aime bien son schéma, c'est assez clair pour les non-initiés! Sur le 3042 de sa clock il met encore 24,3µF tssss c'est une erreur de rookie alors qu'il semble toucher un peu quand mêmehttp://www.dimdim.gr/2017/11/arduino-co ... ac-part-1/

je vais regarder, merci pour les infos

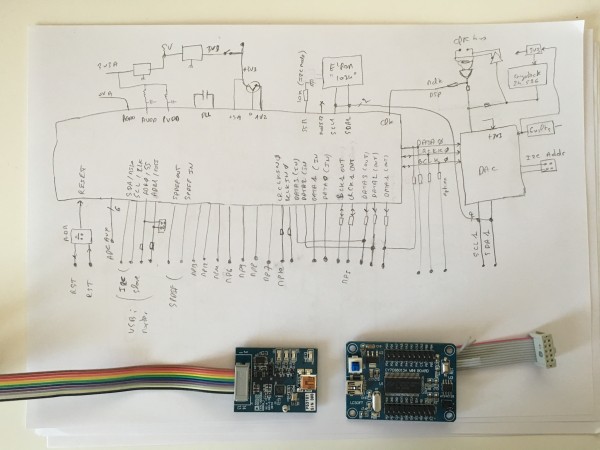

manudrz a écrit:Edit:Les 4493 sont-ils concernés aussi?Speaking of USB to I2S boards, the DAC board has a very specific requirement: The USB board must be able to receive MCLK externally. In other words, the DAC board and USB board must be clocked from the same oscillator. This is due to the AK4490’s design. Unlike the ESS designs which by default run asynchronously, it needs to be on the same clock domain as its I2S sources.

yes sir.

le principe est toujours le même pour les dac ESS : grosso modo ils intègrent un ASRC. donc tu peux avoir 2 domaines de clock différent et dans ce ca la plus précise doit être coté chip DAC. Cela dit dans ce mode, le jitter amont est à priori converti en distorsion par l'asrc..

les AKM n'ont pas d'ASRC donc il leur faut une clock précise coté chip DAC, et le clock domaine pour l'amont doit être le même, donc l'amont doit être slave par rapport à la clock du dac.

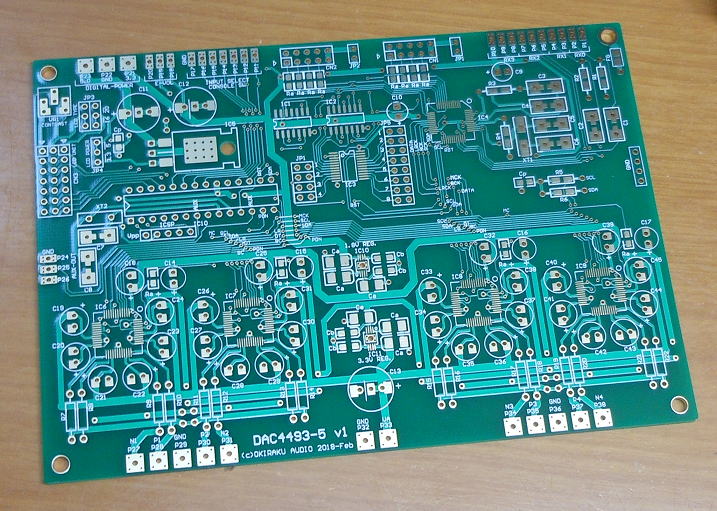

je pense que ma décision est prise de simplifier et de faire une carte alim et horloge de la taille du DAC. Ca permet d'avancer vite et progressivement. je lance les 2 cartes en fabrication en même temps (dac & horloge) comme çà à reception j'ai une soluce qui tourne en I2S avec n'importe quel convertisseur USB-I2S ou en connectant ca à ma carte d'évaluation ADAU1452, ou à un nanoShark ca devrait sortir de la musique.

je pense que ma décision est prise de simplifier et de faire une carte alim et horloge de la taille du DAC. Ca permet d'avancer vite et progressivement. je lance les 2 cartes en fabrication en même temps (dac & horloge) comme çà à reception j'ai une soluce qui tourne en I2S avec n'importe quel convertisseur USB-I2S ou en connectant ca à ma carte d'évaluation ADAU1452, ou à un nanoShark ca devrait sortir de la musique.