Je remets le pied à l'étrier pour me faire un nouveau DAC.

Celui-ci sera basé sur une transmission spdif (plus facile a utiliser que l'i2s) mais avec une attention toute particulière sur le jitter.

Je prévois d'y ajouter un convertisseur usb-spdif pour plus tard.

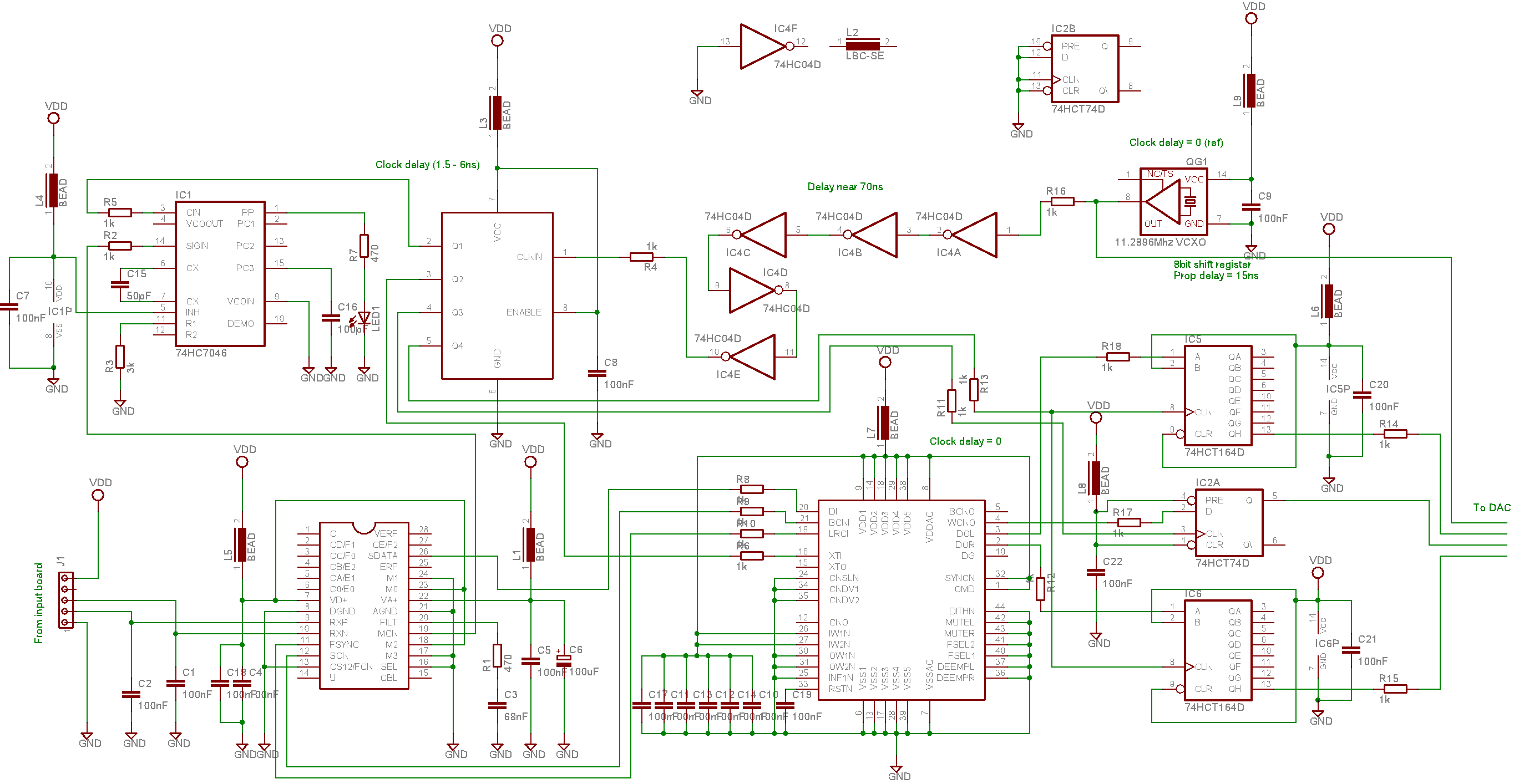

Place au schéma, pas encore terminé :

On retrouve le cs8414 en configuration classique, configuré pour sortir de l'eiaj en 16 bits 44khz.

J'utilise l'horloge récupérée par le cs8414 pour alimenter une pll qui pilotera un vcxo tent labs (filtrage pas encore réalisé), pour s'isoler au maximum du jitter inhérent au spdif.

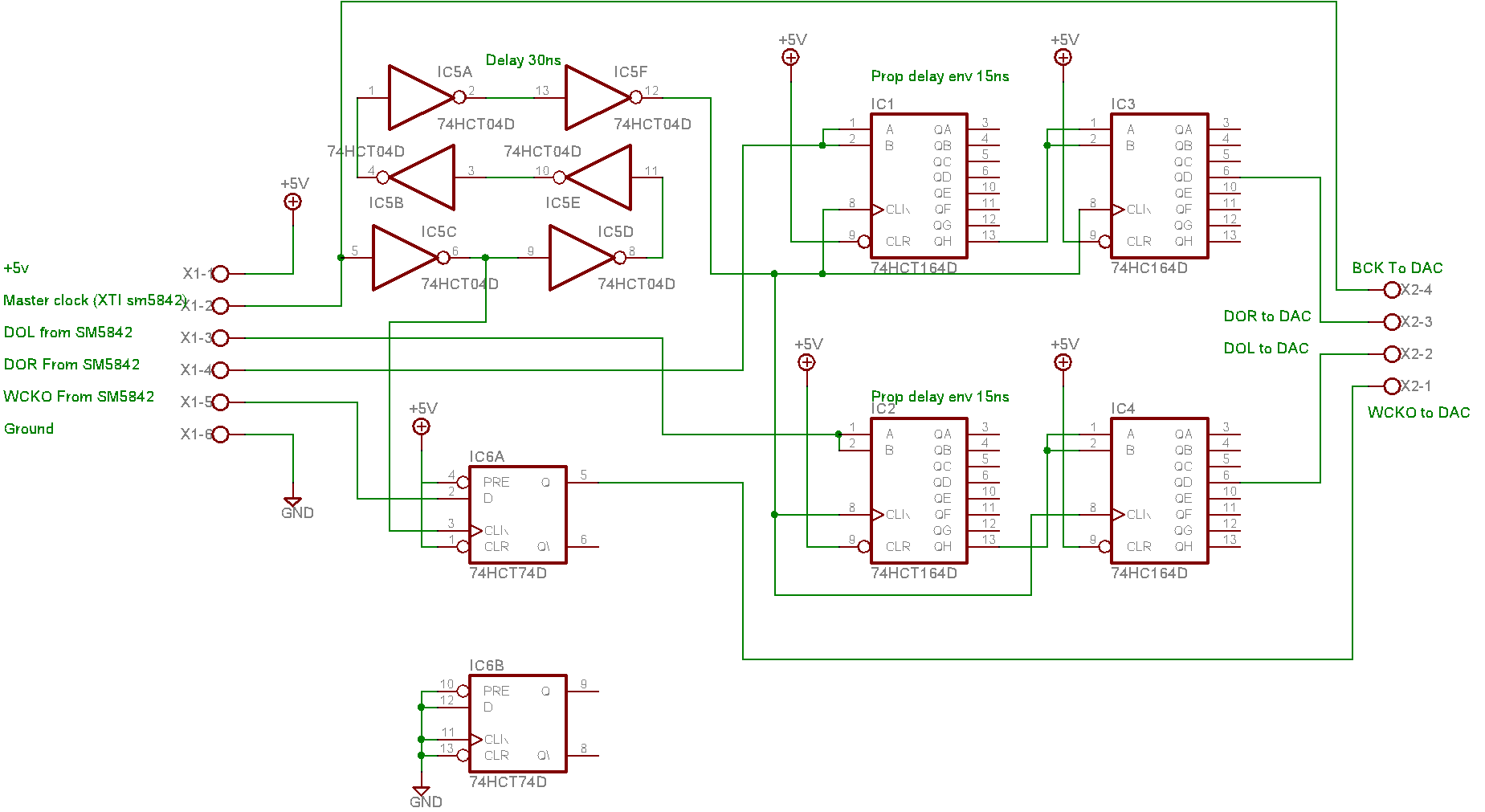

Les données passent ensuite dans le filtre numérique, un SM5847. L'horloge du sm5847 est a 256 x 44.1khz, soit 11.2896mhz. Cela permet d'avoir un bit clock en sortie de filtre (x8) égale au master clock (pll). C'est intéressant car cela permet d'alimenter les dacs directement avec l'horloge qui sort du vcxo (la plus stable).

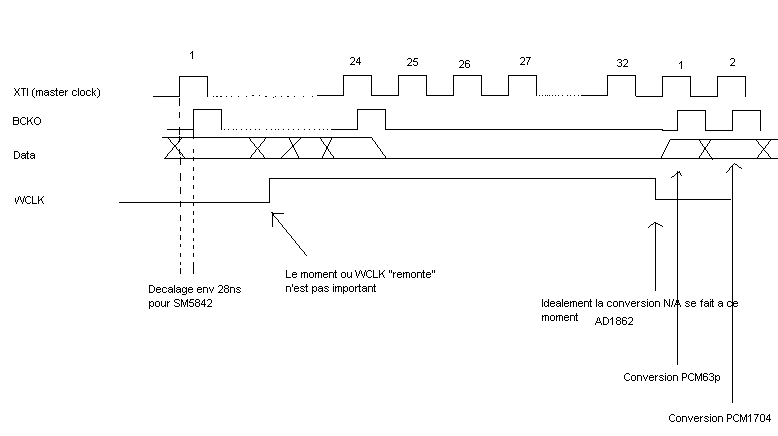

Les deux hc374 permettent de faire un registre à décalage pour décaler les données du sm5847 de 8 périodes d'horloge par rapport au signal wclk. Etant donné que je vais certainement utiliser des pcm1704, le bit clock est le seul signal réellement important, donc pas de reclocking du wclk.

Place aux commentaires !

Je mettrai le design a jour au fur et a mesure de l'avancement et des tests.