salut Alex_twn, un gros travail très méticuleux tant sur la partie routage intégration que R&D/reverse autour du pcm. chapeau. honnêtement je suis extrêmement surpris car pour moi l'implémentation NOS est réductrice puisque le dac fonctionne juste en 6 bits. je m’étais fortement penché sur l'approche de deode et puis je l'avais disqualifié. Par contre l'idée d’utiliser le PCM en en mode filtre externe à 384 ou 768 me semblait plus prometteuse, tu pourras certainement faire les essais dans ce mode avec to FPGA et juger du bénéfice.

Aussi un IV passif à l'avantage d'avoir un temps de réponse instantané, mais l’inconvénient de présenter une tension de modulation qui peux créer une non linéarité dans la réponse des mosfets interne, alors un convertisseur type ad844 me semblait plus approprié. mais bon; tu as tout les éléments en main et le bon niveau pour juger si finalement la solution est bonne à la mesure et si en plus c'est musicalement bon alors parfait! tient nous régulièrement au courant !

est ce que tu as les moyens de mesurer le jitter coté clock et en sortie du fpga ?

|

|

Modérateurs: Modération Forum DIY, Modération Forum Installations, Le Bureau de l’Association HCFR • Utilisateurs parcourant ce forum: Alex_twn et 24 invités

OdroDAC => UGSD

- maxidcx

- Membre HCFR Contributeur

- Messages: 3103

- Inscription Forum: 25 Avr 2007 10:50

Salut Maxidcx,

Merci pour les encouragements.

Pour l'ecoute NOS je ne sais pas dire. Une ecoute I2S standard avec filtres internes actives est tres bonne aussi, au dessus de mon Oppo, j'ai pu faire des tests A/B pour comparer.

Par contre impossible de faire des test A/B en mode standard vs. NOS.

C'est toujours tres bon mais de la a dire si c'est mieux ou pas je ne m'y engage pas pour le moment, pas assez de recul.

La base standard I2S est tres solide et cela marche deja tres bien comme cela, ca je peux l'affirmer.

Le DAC fonctionne en 6-bits en NOS? J'avais loupe ce truc la... pour moi le mode NOS bypass uniquement l'interpolateur 8x mais il n'a aucun effet sur les convertisseurs ICOB ou sigma delta. Peux tu elaborer un peu STP, ca m'interresse de comprendre si je suis passe a cote de quelque chose.

Je pense aussi que les implementations de filtres qu'on peut realiser aujourd'hui dans le FPGA sont probablement meilleures que ceux presents dans le DAC vu qu'il commence un peu a dater.

Donc en effet gain potentiel de ce cote.

Pour le reste ce DAC a des performances excellentes et pour le moment ce que je remarque c'est que si la charge passive ne depasse pas une certaine valeur max on n'ajoute pas de distorsion significative en sortie, tout reste a un tres bon niveau.

Je continue mes tests en effet, je trouve pas mal de lecture interressante qui me permet de correler mes mesures, je commence a connecter les points .

.

Je ne suis malheureusement pas equipe pour mesurer le jitter.

Merci pour les encouragements.

Pour l'ecoute NOS je ne sais pas dire. Une ecoute I2S standard avec filtres internes actives est tres bonne aussi, au dessus de mon Oppo, j'ai pu faire des tests A/B pour comparer.

Par contre impossible de faire des test A/B en mode standard vs. NOS.

C'est toujours tres bon mais de la a dire si c'est mieux ou pas je ne m'y engage pas pour le moment, pas assez de recul.

La base standard I2S est tres solide et cela marche deja tres bien comme cela, ca je peux l'affirmer.

Le DAC fonctionne en 6-bits en NOS? J'avais loupe ce truc la... pour moi le mode NOS bypass uniquement l'interpolateur 8x mais il n'a aucun effet sur les convertisseurs ICOB ou sigma delta. Peux tu elaborer un peu STP, ca m'interresse de comprendre si je suis passe a cote de quelque chose.

Je pense aussi que les implementations de filtres qu'on peut realiser aujourd'hui dans le FPGA sont probablement meilleures que ceux presents dans le DAC vu qu'il commence un peu a dater.

Donc en effet gain potentiel de ce cote.

Pour le reste ce DAC a des performances excellentes et pour le moment ce que je remarque c'est que si la charge passive ne depasse pas une certaine valeur max on n'ajoute pas de distorsion significative en sortie, tout reste a un tres bon niveau.

Je continue mes tests en effet, je trouve pas mal de lecture interressante qui me permet de correler mes mesures, je commence a connecter les points

Je ne suis malheureusement pas equipe pour mesurer le jitter.

- Alex_twn

- Messages: 1093

- Inscription Forum: 10 Nov 2008 6:02

- Localisation: Taiwan

Oh pétard, comment j'ai pu passer à côté ! A suivre et à relire avec grand intérêt !

- gregory_26

- Messages: 1008

- Inscription Forum: 22 Fév 2010 1:08

ouais c'est du lourd!

Alex, j'ai été un peu rapide en parlant de 6 bits.

on parle bien de l'approche qui est décrite dans le DDDAC1794 ?

si oui, son approche est de configurer le dac en mode Mono et filtre externe, en utilisant bclk comme sclk.

effectivement la seule chose qui est by passé c'est ce qui est officiellement appelé l'oversampling.

Mais le résultat c'est que les 24 bits passe dans une moulinette moins lourde (juste le modulateur) et que finalement ca pilote un réseau de 66 sources de courant (d'ou les 6 bits).

Donc il y a un oversampling intrinsèque associé à un noise shapping pour recuperer une dynamique de 120db avec les 6 bits et qui est suposé tourner à 64fs.

Le vrai NOS serait avec le pcm1704 ou AD1865.

Là c'est un flux 24 bits transformé en 6 et ce avec une moulinette réduite, clockée 64x (ou 256/512 avec oversampling).

Je pense en fait que l'oversampling 4x (voire 8x) est important. Certe on peux faire mieux avec le FPGA (site de rutgers.nl entre autre) mais il est indispensable d'upsampler avec une sclk maximale pour tirer toute la dynamique de ce dac 66 niveaux.

mais bon. comme je disais tu as manifestement tous les moyens pour investiguer cela alors il faut que j’arrête la théorie et que tu continue de nous alimenter en feedbacks concret! salut!

Alex, j'ai été un peu rapide en parlant de 6 bits.

on parle bien de l'approche qui est décrite dans le DDDAC1794 ?

si oui, son approche est de configurer le dac en mode Mono et filtre externe, en utilisant bclk comme sclk.

effectivement la seule chose qui est by passé c'est ce qui est officiellement appelé l'oversampling.

Mais le résultat c'est que les 24 bits passe dans une moulinette moins lourde (juste le modulateur) et que finalement ca pilote un réseau de 66 sources de courant (d'ou les 6 bits).

Donc il y a un oversampling intrinsèque associé à un noise shapping pour recuperer une dynamique de 120db avec les 6 bits et qui est suposé tourner à 64fs.

Le vrai NOS serait avec le pcm1704 ou AD1865.

Là c'est un flux 24 bits transformé en 6 et ce avec une moulinette réduite, clockée 64x (ou 256/512 avec oversampling).

Je pense en fait que l'oversampling 4x (voire 8x) est important. Certe on peux faire mieux avec le FPGA (site de rutgers.nl entre autre) mais il est indispensable d'upsampler avec une sclk maximale pour tirer toute la dynamique de ce dac 66 niveaux.

mais bon. comme je disais tu as manifestement tous les moyens pour investiguer cela alors il faut que j’arrête la théorie et que tu continue de nous alimenter en feedbacks concret! salut!

- maxidcx

- Membre HCFR Contributeur

- Messages: 3103

- Inscription Forum: 25 Avr 2007 10:50

Salut Maxidcx,

Oui on parle bien du montage de Deode que tu decris.

J'ai fait les tests en mode NOS et en mode I2S standard et a priori ca marche aussi bien, ceci dit je ne m'engagerai pas sur lequel est le mieux pour le moment.

Pour revenir maintenant a la description que tu donnes concernant la facon dont l'etage current steering est pilote par le DWA, je pense (peut etre a tord) que quel que soit le mode (NOS ou standard), il y a toujours 67 niveaux dans les 2 cas qui pilotent les switch des etages de courant.

Ca ne change rien, juste le seul truc qui peut changer est que le modulateur sigma delta tourne bien en dessous de la frequence a laquelle il devrait le faire et du coup le bruit HF du modulateur se trouve dans dans la bande audio, ce que je vois tres bien avec mes FFT (remontee a presque -100dB a 20KHz, le reste est sous les -140dB entre 0 et 5KHz, a part disto H2 a -120dB). L'effet noise shaping vers les hautes frequences est absent vu la faible frequence du demodulateur.

Donc pour moi cela ne change rien, les etages de courant sont dans tous les cas pilotes sur 67 niveaux, mais encore une fois tu peux tout a fait me contredire car je suis en mode decouverte / reverse engineering et c'est pas simple car les infos donnees par TI sont tres limitees !

J'ai passe du temps a essayer justement de comprendre toutes les valeurs en courant qui sortent en fonction du mot binaire DWA avec generation de mots binaires differents de 1LSB dans le FPGA et c'est loin d'etre simple + on a de belles surprises mais j'arrive en recoupant plusieurs choses a avancer. J'avais tire des premieres conclusions il y a une semaine qui ne sont qu'a moitie justes, c'est beaucoup plus sioux que je pensais (notamment la combinaison des niveaux code ICOB et ceux du sigma delta). Mes tables Excel commencent a devenir relativement complexes...

Au passage si quelqu'un sais comment est genere le code ICOB ca m'aiderait a avancer car je fais des hypotheses.

Dans cette doc http://www.ti.com/lit/an/sbaa042a/sbaa042a.pdf il n'existe pas mais le COB existe et vu que le I de ICOB veux dire inverted COB et que quand on inverse un a un les bits d'un code COB on se trouve avec un code BOB, je me demande si ICOB = BOB...?

Merci !

Oui on parle bien du montage de Deode que tu decris.

J'ai fait les tests en mode NOS et en mode I2S standard et a priori ca marche aussi bien, ceci dit je ne m'engagerai pas sur lequel est le mieux pour le moment.

Pour revenir maintenant a la description que tu donnes concernant la facon dont l'etage current steering est pilote par le DWA, je pense (peut etre a tord) que quel que soit le mode (NOS ou standard), il y a toujours 67 niveaux dans les 2 cas qui pilotent les switch des etages de courant.

Ca ne change rien, juste le seul truc qui peut changer est que le modulateur sigma delta tourne bien en dessous de la frequence a laquelle il devrait le faire et du coup le bruit HF du modulateur se trouve dans dans la bande audio, ce que je vois tres bien avec mes FFT (remontee a presque -100dB a 20KHz, le reste est sous les -140dB entre 0 et 5KHz, a part disto H2 a -120dB). L'effet noise shaping vers les hautes frequences est absent vu la faible frequence du demodulateur.

Donc pour moi cela ne change rien, les etages de courant sont dans tous les cas pilotes sur 67 niveaux, mais encore une fois tu peux tout a fait me contredire car je suis en mode decouverte / reverse engineering et c'est pas simple car les infos donnees par TI sont tres limitees !

J'ai passe du temps a essayer justement de comprendre toutes les valeurs en courant qui sortent en fonction du mot binaire DWA avec generation de mots binaires differents de 1LSB dans le FPGA et c'est loin d'etre simple + on a de belles surprises mais j'arrive en recoupant plusieurs choses a avancer. J'avais tire des premieres conclusions il y a une semaine qui ne sont qu'a moitie justes, c'est beaucoup plus sioux que je pensais (notamment la combinaison des niveaux code ICOB et ceux du sigma delta). Mes tables Excel commencent a devenir relativement complexes...

Au passage si quelqu'un sais comment est genere le code ICOB ca m'aiderait a avancer car je fais des hypotheses.

Dans cette doc http://www.ti.com/lit/an/sbaa042a/sbaa042a.pdf il n'existe pas mais le COB existe et vu que le I de ICOB veux dire inverted COB et que quand on inverse un a un les bits d'un code COB on se trouve avec un code BOB, je me demande si ICOB = BOB...?

Merci !

- Alex_twn

- Messages: 1093

- Inscription Forum: 10 Nov 2008 6:02

- Localisation: Taiwan

Ce soir j'ai joué avec le modulateur sigma delta en vérifiant quelle était la configuration où il fonctionnait le mieux. J'ai appliqué une horloge MCLK externe via mon GBF et observé ce qui se passait à different multiples de Fs. Le shunt MCLK = bclk de Doede n'est pas une si mauvaise chose au final en mode NOS.

Je viens de passer en I2S standard de nouveau (afin d'avoir le niveau de bruit de fond le plus faible possible partout dans la bande audio et faire les meilleurs réglages) et je pense que j'ai trouve les performances optimales de fonctionnement avec l'étage passif en jouant avec Riv, bias et Vdd.

On arrive à 0.0067% de THD et à peu près la même chose en THD+N à 44.1K et 24bits.

La fondamentale est autour de -8dB et ça donne à peu près 1.5VRMS en sortie de transfo asymétrique.

L'élévation de Vdd est indispensable pour atteindre ces meilleures performances mais pas autant que ce que Deode recommande.

Va falloir que j'écoute de nouveau mais une masse de sonde d'oscillo qui s'est détachée de son test point viens de me flinguer un canal. Marche plus qu'en mono pour le moment...

Je viens de passer en I2S standard de nouveau (afin d'avoir le niveau de bruit de fond le plus faible possible partout dans la bande audio et faire les meilleurs réglages) et je pense que j'ai trouve les performances optimales de fonctionnement avec l'étage passif en jouant avec Riv, bias et Vdd.

On arrive à 0.0067% de THD et à peu près la même chose en THD+N à 44.1K et 24bits.

La fondamentale est autour de -8dB et ça donne à peu près 1.5VRMS en sortie de transfo asymétrique.

L'élévation de Vdd est indispensable pour atteindre ces meilleures performances mais pas autant que ce que Deode recommande.

Va falloir que j'écoute de nouveau mais une masse de sonde d'oscillo qui s'est détachée de son test point viens de me flinguer un canal. Marche plus qu'en mono pour le moment...

- Alex_twn

- Messages: 1093

- Inscription Forum: 10 Nov 2008 6:02

- Localisation: Taiwan

Salut Alex-twn, merci par ces retours. c'est intéressant car ce chip m'interresse depuis toujours, il est pus facile à interfacer qu'un AK4497

quand tu parles de mode NOS, donc c'est avec sclk sur bclk, et en désactivant le filtre interne j'imagine.

et si je comprend bien la différence serait sur le noise floor au dessus de 5khz.

pour la thd, il faudrait déjà mesurer aux bornes de la résistance de charge avant le transfo (ou alors il n'y a pas de résistance avant le transfo?) car là ça te fait quand même 25db de moins bon que la spec...

utilises tu le bias 400u sur i ref a base de jfet comme dans la dernière version du dddac?

sinon j'ai jeté un oeil sur le pdf cob, et suite à un mal de crâne je te laisse vérifier l'équation qui sembe valable ICOB=BOB.

quand tu parles de mode NOS, donc c'est avec sclk sur bclk, et en désactivant le filtre interne j'imagine.

et si je comprend bien la différence serait sur le noise floor au dessus de 5khz.

pour la thd, il faudrait déjà mesurer aux bornes de la résistance de charge avant le transfo (ou alors il n'y a pas de résistance avant le transfo?) car là ça te fait quand même 25db de moins bon que la spec...

utilises tu le bias 400u sur i ref a base de jfet comme dans la dernière version du dddac?

sinon j'ai jeté un oeil sur le pdf cob, et suite à un mal de crâne je te laisse vérifier l'équation qui sembe valable ICOB=BOB.

- maxidcx

- Membre HCFR Contributeur

- Messages: 3103

- Inscription Forum: 25 Avr 2007 10:50

Salut Maxidcx,

Oui quand je parle de NOS c'est en effet le mode "external digital filter" du PCM1794A.

Et oui pour MCLK (ou SCLK) = BCLK qui permet de faire tourner le modulateur sigma delta a frequence optimale, je ne sais pas si Deode a fait ces mesures de variation de MCLK comme je l'ai fait afin de comprendre, mais cette astuce de shunter BCLK et MCLK, c'est tres malin de sa part.

C'est a priori le meilleur cas car au dessus le modulateur introduit beaucoup de distorsion et au dessous le SNR diminue (ca se verifie assez bien en regardant le SNR d'un sigma delta en fonction de son ordre + la vitesse xFs a laquelle il tourne, voir Google pour cela).

Et oui tu as bien compris, on a une remontee du bruit a partir de 5KHz dans la bande audio en restant sous les -100dB a 20KHz.

Si tu utilises le filtre d'interpolation interne a ce moment tu deplace le bruit du modulateur (j'imagine car je n'ai pas verifie encore) bien plus haut en frequence et donc pas de remontee dans le spectre audio.

En meme temps ce qui remonte reste toujours sous les -100dB donc c'est relativement faible.

Tout cela pour dire qu'a mon avis en mode NOS ce DAC utilise toujours bien le ICOB + le sigma delta pour faire la meilleure conversion et attaquer l'etage current steering (donc je ne crois pas qu'il y ai perte de resolution sur la valeur analogique du courant de sortie).

Comment calcules tu les 25dB de moins bon que la spec?

Le gros desavantage de l'etage passif est la perte de niveau.

On ajoute des DAC en parallele pour ameliorer cela mais on atteind une limite dure en fonction du nombre de puce, de la valeur du bias, de Riv et de Vdd.

Mes petites experiences / mesures + creation de tables excel me font penser que je sais maintenant trouver les meilleurs points de fonctionnement en fonction de ces parametres (je verifie tout cela en pratique sur board maintenant).

Pour le moment tout semble tres coherent mais je veux tout bien valider afin d'en etre certain.

Le Vdd donne par Deode + Iref n'est pas grave dans le marbre, mes premieres conclusions me font meme penser que c'est un peu excessif. Ca depent fortement de Riv, la symetrie +/- et le nombre de DAC. Ceci dit je suis en revanche convaincu qu'il faut augmenter le Vdd pour atteindre les meilleures performances possibles, car a 5V c'est juste pas possible avec un etage passif.

Je vais passer un peu de temps sur etage actif aussi pour voir ce que cela peut donner.

Je ne veux pas essayer d'AOP, plutot un etage tres simple a JFET.

Juste pour voir et ecouter aussi .

.

Et puis reparer la carte qui a pete ...

Et puis apres s'amuser avec ce qu'on peut faire dans le FPGA......

En tout cas heureux d'avoir tes commentaires sur tout cela.

Oui quand je parle de NOS c'est en effet le mode "external digital filter" du PCM1794A.

Et oui pour MCLK (ou SCLK) = BCLK qui permet de faire tourner le modulateur sigma delta a frequence optimale, je ne sais pas si Deode a fait ces mesures de variation de MCLK comme je l'ai fait afin de comprendre, mais cette astuce de shunter BCLK et MCLK, c'est tres malin de sa part.

C'est a priori le meilleur cas car au dessus le modulateur introduit beaucoup de distorsion et au dessous le SNR diminue (ca se verifie assez bien en regardant le SNR d'un sigma delta en fonction de son ordre + la vitesse xFs a laquelle il tourne, voir Google pour cela).

Et oui tu as bien compris, on a une remontee du bruit a partir de 5KHz dans la bande audio en restant sous les -100dB a 20KHz.

Si tu utilises le filtre d'interpolation interne a ce moment tu deplace le bruit du modulateur (j'imagine car je n'ai pas verifie encore) bien plus haut en frequence et donc pas de remontee dans le spectre audio.

En meme temps ce qui remonte reste toujours sous les -100dB donc c'est relativement faible.

Tout cela pour dire qu'a mon avis en mode NOS ce DAC utilise toujours bien le ICOB + le sigma delta pour faire la meilleure conversion et attaquer l'etage current steering (donc je ne crois pas qu'il y ai perte de resolution sur la valeur analogique du courant de sortie).

Comment calcules tu les 25dB de moins bon que la spec?

Le gros desavantage de l'etage passif est la perte de niveau.

On ajoute des DAC en parallele pour ameliorer cela mais on atteind une limite dure en fonction du nombre de puce, de la valeur du bias, de Riv et de Vdd.

Mes petites experiences / mesures + creation de tables excel me font penser que je sais maintenant trouver les meilleurs points de fonctionnement en fonction de ces parametres (je verifie tout cela en pratique sur board maintenant).

Pour le moment tout semble tres coherent mais je veux tout bien valider afin d'en etre certain.

Le Vdd donne par Deode + Iref n'est pas grave dans le marbre, mes premieres conclusions me font meme penser que c'est un peu excessif. Ca depent fortement de Riv, la symetrie +/- et le nombre de DAC. Ceci dit je suis en revanche convaincu qu'il faut augmenter le Vdd pour atteindre les meilleures performances possibles, car a 5V c'est juste pas possible avec un etage passif.

Je vais passer un peu de temps sur etage actif aussi pour voir ce que cela peut donner.

Je ne veux pas essayer d'AOP, plutot un etage tres simple a JFET.

Juste pour voir et ecouter aussi

Et puis reparer la carte qui a pete ...

Et puis apres s'amuser avec ce qu'on peut faire dans le FPGA......

En tout cas heureux d'avoir tes commentaires sur tout cela.

- Alex_twn

- Messages: 1093

- Inscription Forum: 10 Nov 2008 6:02

- Localisation: Taiwan

Salut!

excellente info donc tu recommandes d'attaquer ce dac avec bclk=sck et de ne pas utiliser le DF interne.

on peux toujours voir ce que ca donne ensuite avec un upsampling 4x / 192k en amont par exemple avec l'asrc d'un DSP ou dans ton FPGA bien sur.

la spec donne 0.0004% thd donc -108db

tu mesure 0.0067% donc -84db, doc delta 24db

mais il faut vérifier si ton matériel de mesure est transparent pour cette mesure

je viens de relire cette page:

https://www.by-rutgers.nl/IV-converter.html

et ce pdf:

https://www.by-rutgers.nl/PDFiles/Matur ... verter.pdf

je pense que l'approche ampli op restera la meilleure mais rien n'empeche de garder un transfo en sortie

mais rien n'empeche de garder un transfo en sortie

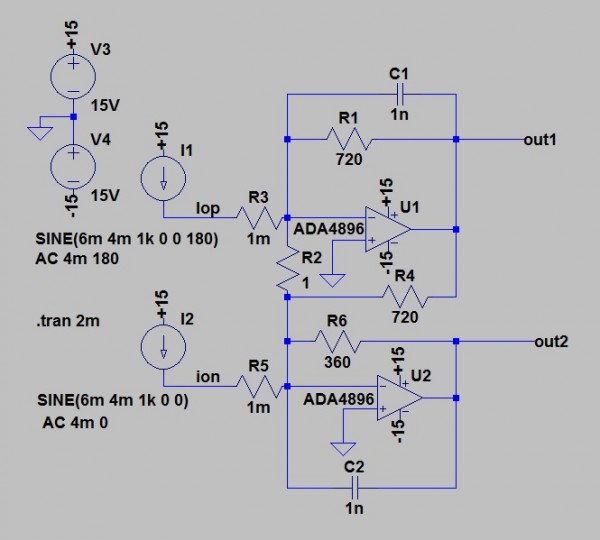

tu pourrais essayer ca vite fait, ca te ressort la tension centrée sur 0 en out 2 (soustraction faite en courant via R4)

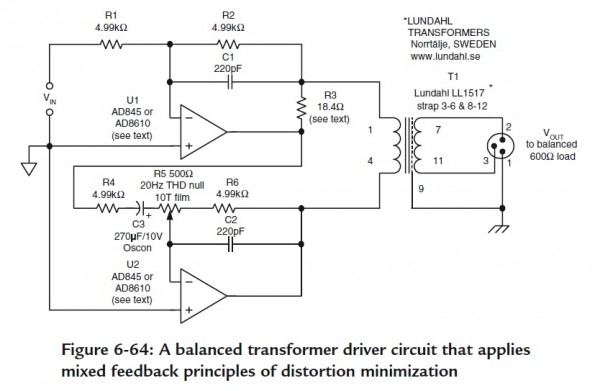

et pour ton transfo, il faudrait chiader un peu pour t"assurer qu'il n'apporte pas de distorsion, par exemple avec ce montage proposé par walt jung (ICI) l'idée c'est d'avoir un feedback positif sur la mesure du courant qui traverse le transfo

Alex_twn a écrit:Et oui pour MCLK (ou SCLK) = BCLK qui permet de faire tourner le modulateur sigma delta a frequence optimale

C'est a priori le meilleur cas car au dessus le modulateur introduit beaucoup de distorsion et au dessous le SNR diminue

Tout cela pour dire qu'a mon avis en mode NOS ce DAC utilise toujours bien le ICOB + le sigma delta pour faire la meilleure conversion et attaquer l'etage current steering (donc je ne crois pas qu'il y ai perte de resolution sur la valeur analogique du courant de sortie).

excellente info donc tu recommandes d'attaquer ce dac avec bclk=sck et de ne pas utiliser le DF interne.

on peux toujours voir ce que ca donne ensuite avec un upsampling 4x / 192k en amont par exemple avec l'asrc d'un DSP ou dans ton FPGA bien sur.

Alex_twn a écrit:Comment calcules tu les 25dB de moins bon que la spec?

la spec donne 0.0004% thd donc -108db

tu mesure 0.0067% donc -84db, doc delta 24db

mais il faut vérifier si ton matériel de mesure est transparent pour cette mesure

Alex_twn a écrit:Je vais passer un peu de temps sur etage actif aussi pour voir ce que cela peut donner.

Je ne veux pas essayer d'AOP, plutot un etage tres simple a JFET.

Juste pour voir et ecouter aussi.

Et puis reparer la carte qui a pete ...

Et puis apres s'amuser avec ce qu'on peut faire dans le FPGA......

En tout cas heureux d'avoir tes commentaires sur tout cela.

je viens de relire cette page:

https://www.by-rutgers.nl/IV-converter.html

et ce pdf:

https://www.by-rutgers.nl/PDFiles/Matur ... verter.pdf

je pense que l'approche ampli op restera la meilleure

tu pourrais essayer ca vite fait, ca te ressort la tension centrée sur 0 en out 2 (soustraction faite en courant via R4)

et pour ton transfo, il faudrait chiader un peu pour t"assurer qu'il n'apporte pas de distorsion, par exemple avec ce montage proposé par walt jung (ICI) l'idée c'est d'avoir un feedback positif sur la mesure du courant qui traverse le transfo

- maxidcx

- Membre HCFR Contributeur

- Messages: 3103

- Inscription Forum: 25 Avr 2007 10:50

maxidcx a écrit:Salut!

la spec donne 0.0004% thd donc -108db

tu mesure 0.0067% donc -84db, doc delta 24db

mais il faut vérifier si ton matériel de mesure est transparent pour cette mesure

Je vois. Mais c'est pas si direct que ca comme comparaison. TI donne 0.0004% a 0dB, j'ai 0.0067% a -8.9dB... Comme je disais l'etage passif est tres dur a driver et on atteind une limite. Avec un etage actif je suis persuade que je peux aller titiller les perf de la datasheet, en passif je suis a mon avis proche des meilleures disto a obtenir.

Je viens de reverifier la calibration de mon systeme de mesure, a priori tout est bon et je sais mesurer jusqu'a 0.0005~0.0006% de THD+N donc j'ai encore de la marge.

Merci pour les liens.

- Alex_twn

- Messages: 1093

- Inscription Forum: 10 Nov 2008 6:02

- Localisation: Taiwan

mais alors pourquoi s'acharner avec l'étage passif/resistif ? moins bruyant ?

- maxidcx

- Membre HCFR Contributeur

- Messages: 3103

- Inscription Forum: 25 Avr 2007 10:50

Salut Maxidcx,

Pour l'instant je ne sais pas encore dire, en tout cas avec le niveau de disto de l'etage passif, les ecoutes sont de bonne qualite comme explique auparavant.

C'est un projet en constante evolution dans lequel je veux tester plusieurs solutions et pour l'instant je suis sur cet etage resistif simplissime.

Au passage si etage actif, il ne sert a rien je pense de mettre plusieurs DAC en parallele ca n'a pas trop de sens.

J'ai decouvert un pb avec les transfos de sortie hier, il va falloir que je me mette a examiner cela en detail.

Pour l'instant je ne sais pas encore dire, en tout cas avec le niveau de disto de l'etage passif, les ecoutes sont de bonne qualite comme explique auparavant.

C'est un projet en constante evolution dans lequel je veux tester plusieurs solutions et pour l'instant je suis sur cet etage resistif simplissime.

Au passage si etage actif, il ne sert a rien je pense de mettre plusieurs DAC en parallele ca n'a pas trop de sens.

J'ai decouvert un pb avec les transfos de sortie hier, il va falloir que je me mette a examiner cela en detail.

- Alex_twn

- Messages: 1093

- Inscription Forum: 10 Nov 2008 6:02

- Localisation: Taiwan

Alex_twn a écrit:Salut Maxidcx,

Au passage si etage actif, il ne sert a rien je pense de mettre plusieurs DAC en parallele ca n'a pas trop de sens.

je suis daccord, ça réduit juste le bruit de 3db, mais déjà utiliser un PCM en mode Mono ç'est pas mal. 130db il faut assumer pour les étages suiveurs!

- maxidcx

- Membre HCFR Contributeur

- Messages: 3103

- Inscription Forum: 25 Avr 2007 10:50

je vois que tu as utilisé un 3042 pour l'alim du Dac; sur le dernier DDDAC il utilise un shunt sur base tentlabs. je me demande si ca a un interret du fait que la conso du dac en courant semble etre constante quelque soit le code, by design. ou alors il y a peut etre quelques glitch à la commutation mais dans ce cas le découplage fait l'affaire. Est ce que tu aurais fait/pourrais faire une mesure de la variation du VDAC en fonction d'un sweep sur la sortie du DAC ? ca donnerait une représentation de l'impédance de l'alim

- maxidcx

- Membre HCFR Contributeur

- Messages: 3103

- Inscription Forum: 25 Avr 2007 10:50

C'est fiable les shunts sur la durée ? Notre vieille Nazarette chauffait un max, chez moi en tout cas... LT3042 c'est déjà du top niveau. T'as un DSPiy Maxidcx?

- manudrz

- Messages: 1415

- Inscription Forum: 28 Déc 2010 0:25

- Localisation: 50540

|

|